ASIC 流程、合成( synthesis )、STA、Genus 工具流程、Tempus 流程、Innovus 流程實體設計、實體驗證( Physical design )

從這 40.5 小時的課程,你會學到

- ASIC流程簡介

- 邏輯合成與實體合成

- 時間概念、定義

- 靜態時序分析(Static Timing Analysis,STA)

- 時序路徑、約束、模式

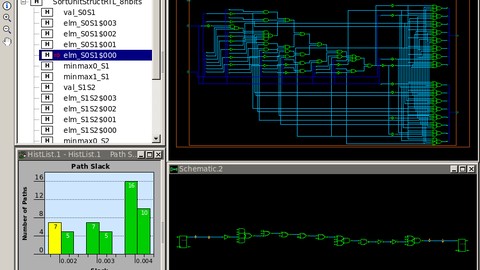

- 使用 Genus 工具執行合成範例

- 使用 Tempus 工具執行 STA 範例

- 使用 Innovus 工具的實體設計流程

- 平面圖( Floorplan )

- 放置( Placement )

- 時鐘樹合成(Clock Tree Synthesis ,CTS)

- 路由

要求

- 使用 Verilog 進行 RTL 設計的基礎知識

- 數位基礎知識

- Verilog 語言

課程說明

第 1 部分:合成與靜態時序分析 (STA)

本課程適合想要獲得 ASIC 合成和 STA 知識的各個級別的學生。

想要實習的電子專業學生、想要在 VLSI 領域開始職涯的工程師。

本課程涵蓋以下章節:

- ASIC 流程簡介

- 邏輯合成 第一部分 – 合成的輸入與輸出、合成約束、程式庫( libraries )

- 邏輯合成第二部分 – 使用 Cadence Genus 工具流程的合成演示

- 實體合成 – 各種檔案格式和描述,出入口( gates )的實體尺寸

- 時間概念 – 建立時間、保持時間、鬆弛時間。違規、時間預算

- 靜態時序分析

- 時序路徑 – 時脈到輸出、傳播延遲、輸入延遲、輸出延遲等,STA 使用 Cadence Tempus 工具流

- 時間限制和各種模式 – MMMC

- 時序異常-錯誤路徑、多循環路徑

第 2 部分:實體設計

- 實體設計的輸入

- Innovus 工具步驟

- 平面圖

- 平面圖演示

- 放置

- CTS

- CTS 演示

- 路由

- SDC_MMMC_PVT角

- 實體驗證

本課程適合想要獲得 ASIC 合成和 STA 知識的各個級別的學生。

想要實習的電子專業學生、想要在 VLSI 領域開始職涯的工程師。

本課程涵蓋以下章節:

所有主題均透過詳細的例子進行闡述,並在需要時以圖表進行說明。

清晰的解釋;課程結束時添加的作業用於練習實際操作範例。

講座由 VLSI 行業的實踐者講授,他們曾參與過多個專案並完成過晶片

為了更好地理解課程內容,請親自動手使用工具(您所在的機構/公司可能有提供)。

一切順利 – 學習愉快

目標受眾

- 實習 – 具有 ECE/EEE 背景的 BE/BTech/MTech 學生和工程師

- 想要在 ASIC 後端活動中開始 VLSI 職業生涯的初學者

講師簡介

VLSI Mentor 超大規模積體電路

- 擁有 20 多年 ASIC 設計和驗證經驗,並負責端對端晶片設計。

- VLSI 設計服務公司 Excel VLSI 的創辦人

- 豐富的 ASIC 設計和驗證執行技能,並具有以下實務經驗:

o IP/Block 設計驗證使用 – Verilog、System Verilog 和 UVM

o VIP 發展

o 程式碼覆蓋率和功能覆蓋率指標。

o 制定測試計劃和基於隨機/方法的測試環境

o 使用 C/C++ 進行 SoC 驗證

o 晶片級閘級模擬

o 工具流的自動化腳本。

字幕:英文

- 想要了解如何將英文字幕自動翻譯成中文? 請參考這篇 How-To

- Udemy 永久擁有課程 NT310 起特價中(點擊連結看更多)

- ✨年訂閱每月 NT350 🌈 悠遊 Udemy 的 26000+ 門課,最大化學習 ( 原價 NT635/月 )

- Udemy 現在越來越多課程有中文字幕,請參考 Soft & Share 中文線上課程

- 手機上點選優惠連結看到的價格比電腦上看到的貴

- $代表當地貨幣, 如在台灣為 NT

- 點選”報名參加課程”有可能因瀏覽器 cookies 轉久一點或回報錯誤而無法連上,請稍等刷新或重新點選就會出現

報名參加課程

也許你會有興趣

- 半導體相關線上課程

- ★英語學習地圖 – 練好英文是最大的學習槓桿

- 如何找工作學習地圖 – 找工作不要靠運氣!

- 從 Soft & Share 各種社團頻道挑選你喜歡的加入

發表迴響