SystemVerilog 語言建構基礎知識

從這 14 小時的課程,你會學到

- RTL 驗證的 SystemVerilog 基礎知識

- 針對 FPGA 工程師的 OOP 基礎知識

- 約束隨機驗證方法的基礎知識

- 分層測試平台架構的基礎知識

- 建立發電機、驅動程式、監視器、記分板、環境類

- SV 的陣列、佇列、動態陣列、任務和方法

- SV 的進程間通訊和隨機化

要求

Verilog 和數位電子基礎知識

課程說明

VLSI 產業分為兩個流行的分支,即。系統設計和系統驗證。 Verilog、VHDL 仍然是該領域大多數設計工程師的熱門選擇。不過,可以使用硬體描述語言來進行初步的功能驗證。硬體描述語言執行程式碼覆蓋率分析、極端情況測試等的能力有限,事實上有時不可能使用 HDL 執行此檢查。

因此,專業驗證語言(例如 SystemVerilog)開始成為設計驗證的主要選擇。

SystemVerilog 物件導向的特性允許繼承、多態性等功能,增加了在設計中尋找 HDL 根本無法找到的關鍵錯誤的功能。

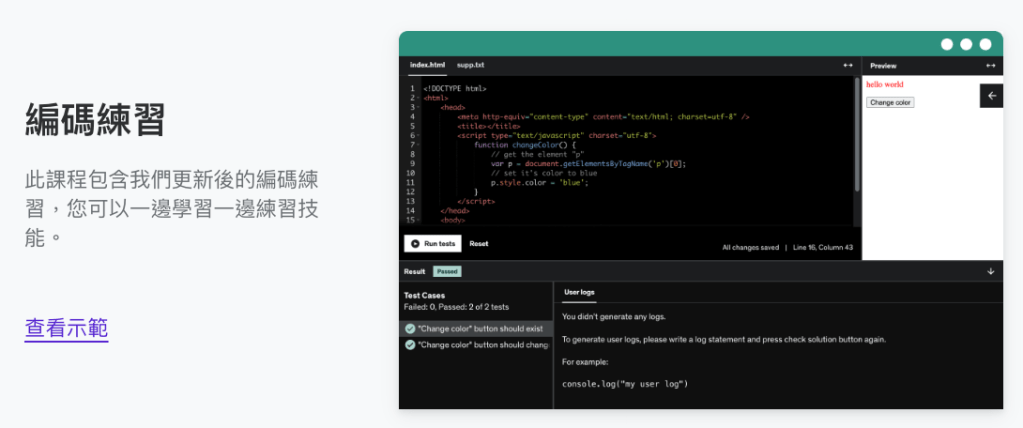

與設計數位系統相比,驗證當然更加棘手和有趣,因此它由大量 OOP 構造組成,而不是 Verilog。 SystemVerilog 是數位系統驗證驗證工程師中最受歡迎的選擇之一。本旅程將帶您了解用於編寫 SystemVerilog 測試平台和執行晶片驗證的最常用技術。課程的結構使得任何希望學習 System Verilog 的人都能夠理解一切。最後,實踐是成為專家的關鍵。

目標受眾

任何希望遷移到 SystemVerilog Testbench 進行 RTL 驗證的人

講師簡介

Kumar Khandagle 培訓師 @ NAMASTE FPGA ( 講師更多課程 )

我目前在 NAMASTE FPGA 線上學習平台擔任講師,負責為本科生和研究生創建教育內容。該內容旨在幫助他們掌握VLSI(超大規模整合)技術的最新趨勢。在此之前,我曾在印度頂尖金融科技公司之一擔任 FPGA 開發主管。在那裡,我領導一個團隊利用 Xilinx Alveo FPGA 卡開發了尖端的高頻交易平台。

在涉足金融科技產業之前,我在印度孟買大學擔任了三年的 VLSI 培訓師。此外,我還在印度一家專注於應用電子研究的著名研發中心擔任了一年的研究科學家。在此期間,我為一些專案做出了重大貢獻,例如為本土 MRI 機器開發 FPGA 上的梯度控制器和 64 MHz 接收器。

在閒暇時間,我熱衷於創建 Udemy 課程,並且還與 Larsen & Toubro Technology Services 和 Power International 等組織合作。在這些合作中,我在設計各種基於 FPGA 的系統中發揮了關鍵作用,包括同步 DAQ、多通道邏輯分析儀和資料傳輸系統 ( Data Transmission Systems,DTS )。我的主要專業知識和興趣領域圍繞著前端 VLSI 設計、系統單晶片 ( System-on-Chip,SoC ) 開發和晶片驗證。

英文字幕:有

- 想要了解如何將英文字幕自動翻譯成中文? 請參考這篇 How-To

- Udemy 永久擁有課程 課程特價中 約 NT350 (點擊連結看更多)

- ✨年訂閱每月 NT350 🌈 悠遊 Udemy 的 26000+ 門課,最大化學習 ( 原價 NT635/月 )

- Udemy 現在越來越多課程有中文字幕,請參考 Soft & Share 中文線上課程

- 手機上點選優惠連結看到的價格比電腦上看到的貴

- $代表當地貨幣, 如在台灣為 NT

- 點選”報名參加課程”有可能因瀏覽器 cookies 轉久一點或回報錯誤而無法連上,請稍等刷新或重新點選就會出現

報名參加課程

也許你會有興趣

- FPGA 相關線上課程

- ★英語學習地圖 – 練好英文是最大的學習槓桿

- 如何找工作學習地圖 – 找工作不要靠運氣!

- 從 Soft & Share 各種社團頻道挑選你喜歡的加入

發表迴響